���ߣ� ����늙C(j��)�������������� T. Murakami K. Sadamatsu M. Imaizumi E. Suekawa

����늙C(j��)�ȶ˼��g(sh��)�о����� S.Hino

����늙C(j��)�ȶ˼��g(sh��)�о����� S.Hino

����늙C(j��)���m(x��)����،�(du��)����SiC SBD��Schottky Barrier Diode����SiC MOSFETоƬ�M(j��n)���аl(f��)��MOSFET�cSBD������ͬһоƬ��������ʡ���m(x��)�����O�ܲ�ʹģ�K�����p�O�����������˻������Č�(du��)3.3kV����SiC SBD��SiC MOSFET늚������M(j��n)�����о����͂��y(t��ng)3.3kV SiC MOSFET�M(j��n)���ˌ�(du��)��������Ҫ늚Ⅲ��(sh��)����JDS-VDS�����������Լ��_(k��i)�P(gu��n)���ζ��](m��i)�����@�ą^(q��)�e���@��ζ��ʹ�ü���SBD��SiC MOSFET���g(sh��)�ϵK��С���ѽ�(j��ng)ȡ�õ��о��Y(ji��)������������SiC SBD��SiC MOSFET����һ���߉�SiC����ģ�K���кܺõđ�(y��ng)��ǰ����

1 ����

����늙C(j��)�ѽ�(j��ng)�ɹ��،�(sh��)�F(xi��n)��3.3kVȫSiC����ģ�K�̘I(y��)����ԓģ�K���Â��y(t��ng)��SiC MOSFET�ͷ���(li��n)SBD����(y��ng)�����F������׃������[1,2]����һ�����҂����ڞ���һ��3.3kV SiCģ�K�_(k��i)�l(f��)����SBD��MOSFET[3,4]���c���y(t��ng)SiC MOSFET���������SBD��SiCMOSFET����ʡ������ģ�K��(n��i)�����m(x��)�����O��������SiC MOSFET���w���O�������(d��o)�µ��p�O�˻������Č�(du��)���y(t��ng)SiC MOSFET�ͼ���SBD��SiCMOSFET��늚������M(j��n)���ˌ�(du��)���о����Y(ji��)����������SBD��SiCMOSFET����һ��3.3kVȫSiC����ģ�K���кܺõđ�(y��ng)��ǰ����

2 MOSFET�Y(ji��)��(g��u)

�D1��3.3kV���y(t��ng)SiC MOSFET�ͼ���SBD��SiC MOSFETоƬ����D����(du��)�ڼ���SBD��SiC MOSFET����MOSԪ����(n��i)Ƕ��������������^(gu��)��SBD늘O�������ļ���SBD�O(sh��)Ӌ(j��)������ȫ�����p�O����������pС©����������M(j��n)�Ќ�(du��)�����҂���������ͬ��Ч��e�Ă��y(t��ng)SiC MOSFET�ͼ���SBD��SiCMOSFETоƬ��

�D1 ���y(t��ng)MOSFET�ͼ���SBD��MOSFET����D

3 ����(sh��)��(du��)��

3.1 �o�B(t��i)����(sh��)

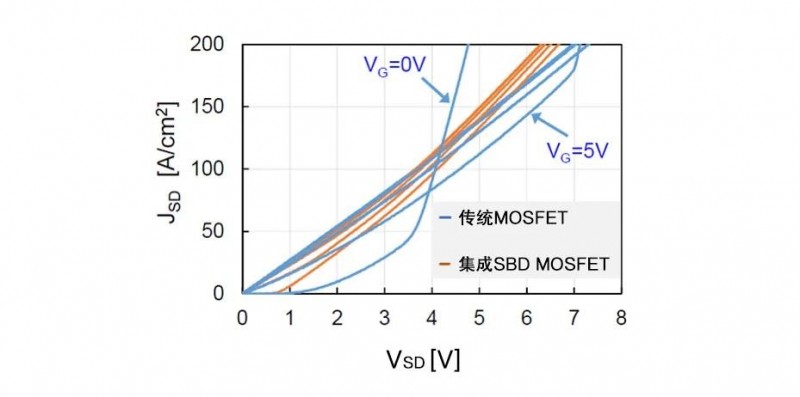

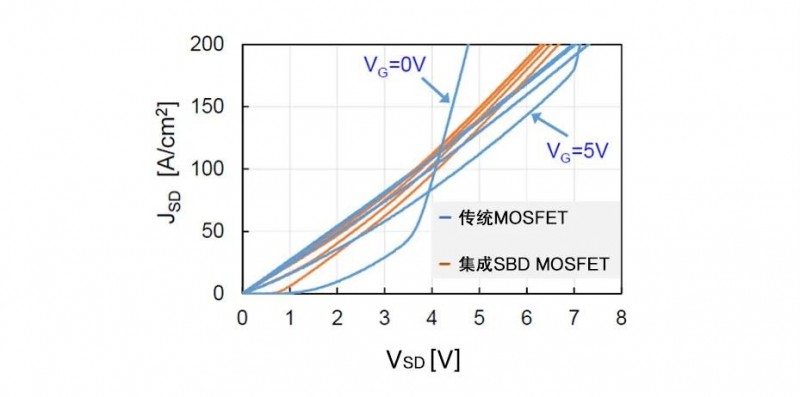

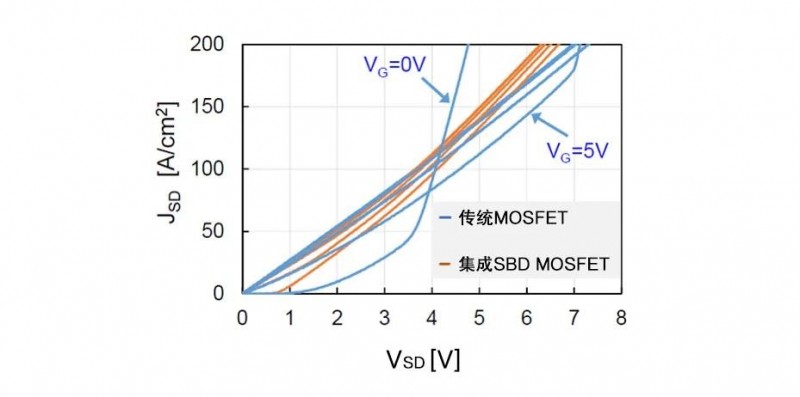

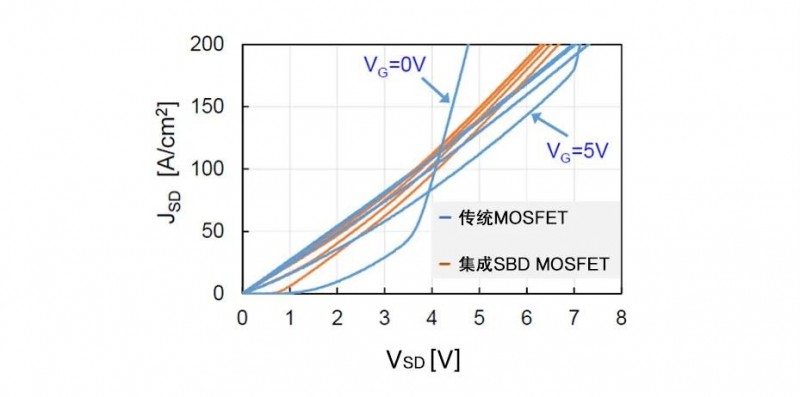

�D2����y(t��ng)SiC MOSFET�c����SBD��SiC MOSFET��175��l�����������ԅ���(sh��)�Č�(du��)�����D��չʾ���ڲ�ͬ�ŘO늉��l���µ�JDS-VDS�������䌧(d��o)ͨ���Ȃ��y(t��ng)SiC MOSFET����һЩ���@����?y��n)�����ͬ����Ч��e�����c���y(t��ng)SiC MOSFET���������SBD��SiC MOSFET��MOS�ϵ�����ҪСһЩ����(y��ng)ԓע����Ǽ���SBD��SiC MOSFETͨ�B(t��i)������������(du��)�^С���@����?y��n)�Ф�ػ������^�ߵ�ͨ��������ʹ��SBD����e����(du��)��С���D3����y(t��ng)SiC MOSFET�c����SBD��SiC MOSFET�ڽY(ji��)��175��͖ŘO����ƫ�×l���·���?q��)�ͨ���ԵČ?du��)������?y��n)�Y(ji��)늈�(ch��ng)�ֲ���ͬ���ɗlJSD-VSD�������в�ͬ�Ĺ��c(di��n)늉������ڃɷN�d���Ӆ��c��(d��o)늣����y(t��ng)SiC MOSFET�ķ���?q��)�ͨ���׃����С�?/div>

�D2 ����?q��)�ͨ���ԣ?75�棩

�D3 ����?q��)�ͨ���ԣ?75����VGS=-7V��

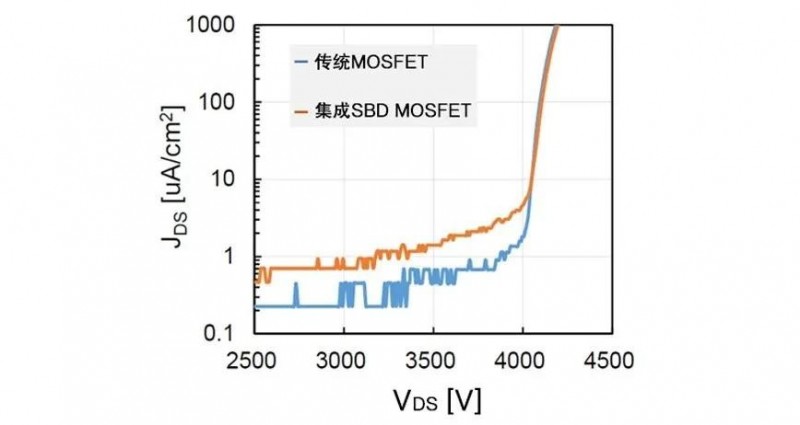

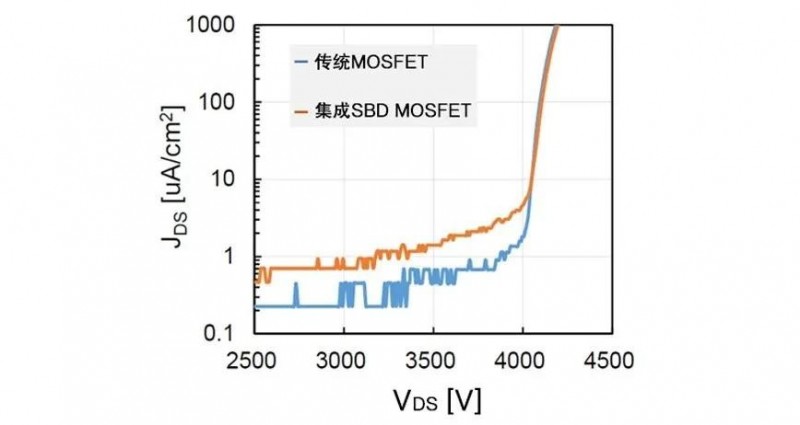

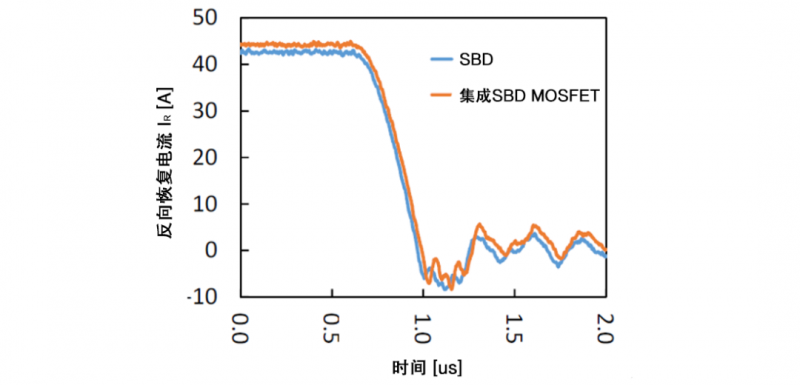

�D4����y(t��ng)SiC MOSFET�ڽY(ji��)��175��͖ŘO����ƫ�×l���µķ���?q��)�ͨ��������?y��n)鼯��SBD��SiC MOSFET����?q��)�ͨ�����MOSFET�ϵ��cSBD֮�������Է�������ܶ�JSD��(du��)�ŘO늉�����ه������(du��)�^С���D5����y(t��ng)SiC MOSFET�c����SBD��SiC MOSFET��25��l����?li��n)������Ԍ?du��)�������Կ�������SBD��SiC MOSFET©�O©������ܺõ����������c���y(t��ng)SiC MOSFET��ͬһˮƽ��

�D4 ����?q��)�ͨ���ԣ?75����VGS=0~17V��

�D5 �������ԣ�25����VGS=-10V��

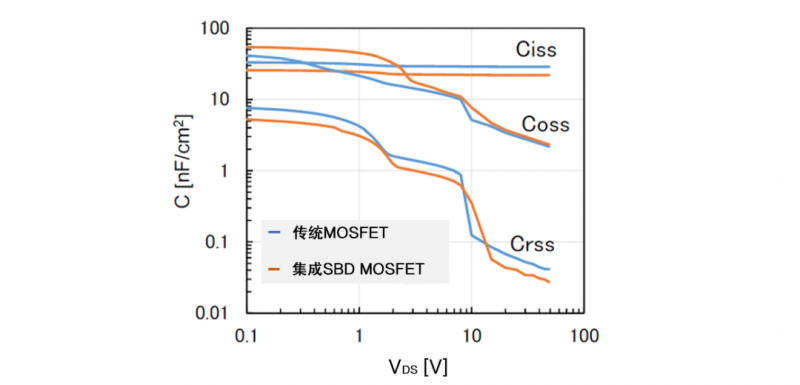

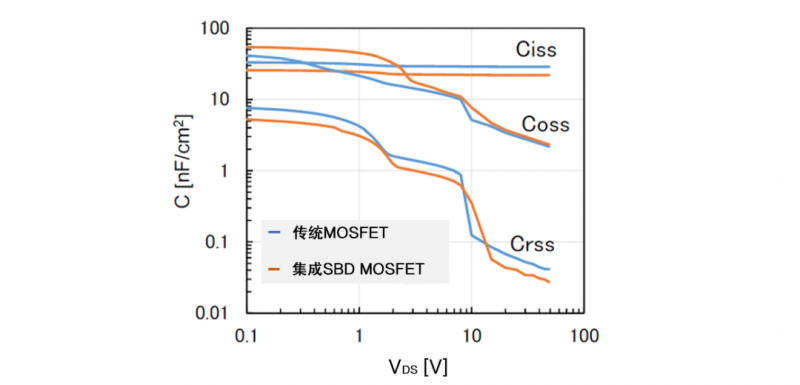

�D6����y(t��ng)SiC MOSFET�c����SBD��SiC MOSFET���l��100kHz���ضȞ�25��l���O�g����cVDS֮�g���P(gu��n)ϵ��������(du��)��ݔ����ݣ�Ciss���ͷ�����ݣ�Crss��, ���y(t��ng)SiC MOSFET���ڼ���SBD��SiC MOSFET���@���ɶྦྷ��늘O��(c��)��JFET�ı����ܶȲ��ɵ�����(du��)��ݔ����ݣ�Coss��, ����SBD��SiC MOSFET���ڂ��y(t��ng)SiC MOSFET���@����?y��n)鼯��SBD��MOSFET Cossֵ����y(t��ng)SiC MOSFET�cSBD��Coss֮����

�D6 �O�g���VS VDS��25����100kHz��

3.2 ��(d��ng)�B(t��i)����(sh��)

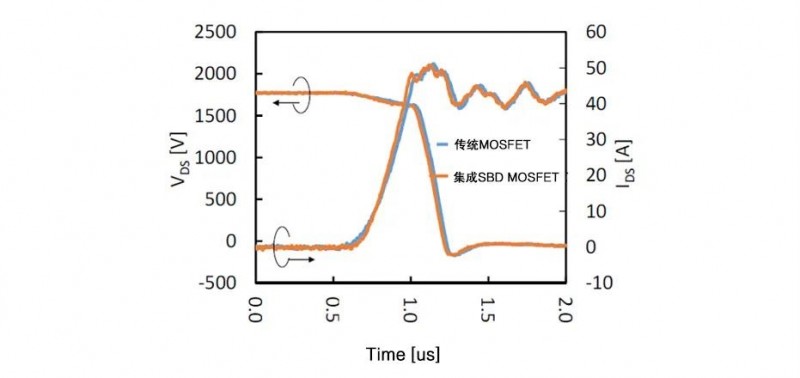

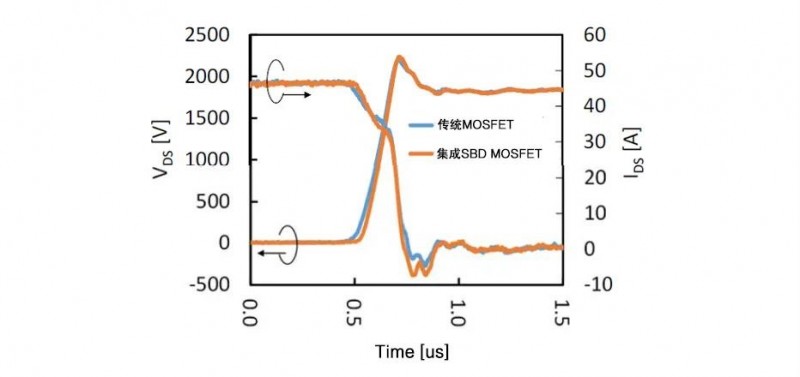

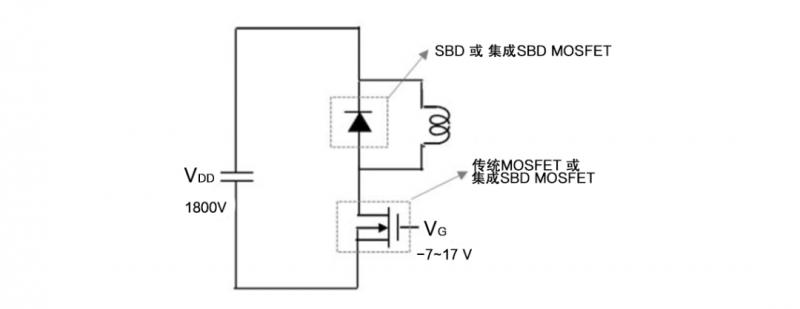

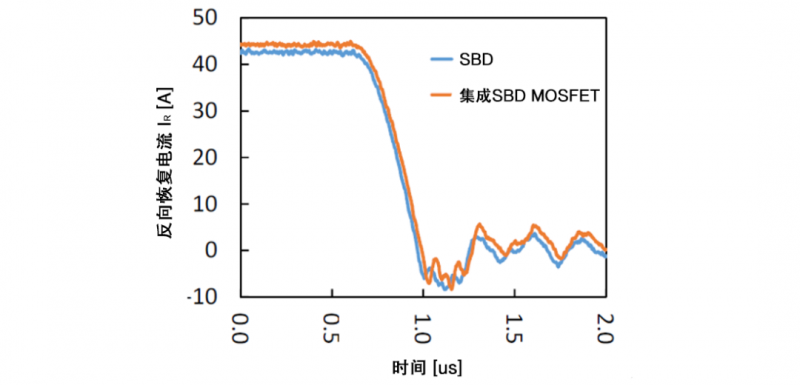

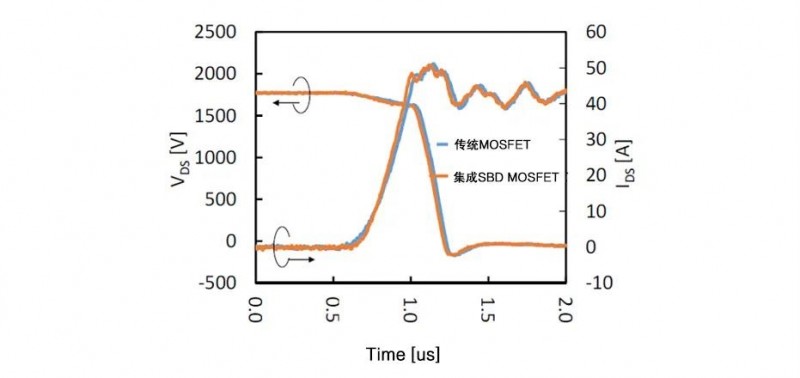

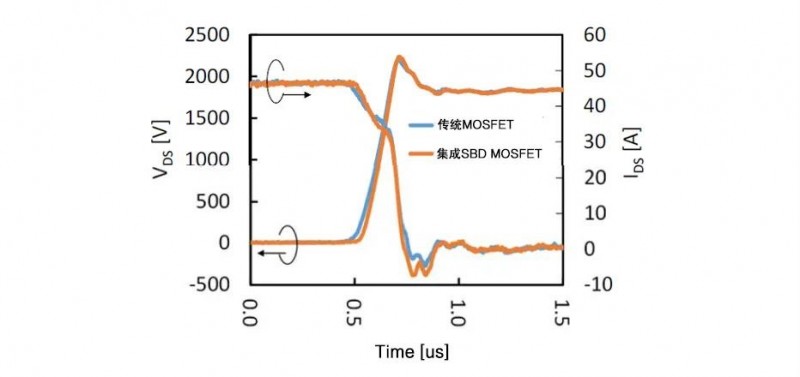

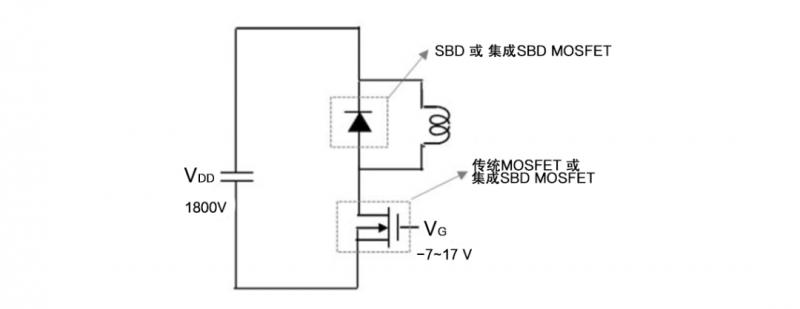

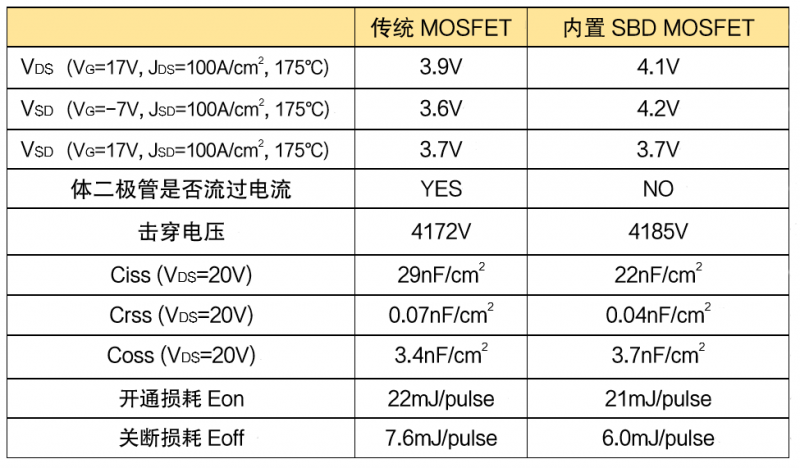

�D7�͈D8�������p�}�_�y(c��)ԇ����175���y(c��)�õ��_(k��i)�P(gu��n)�������D9��y(c��)ԇ�·���ڜy(c��)ԇ����VDD�O(sh��)����1800V��VGS�O(sh��)�Þ�-7/17V��ͨ�^(gu��)�{(di��o)���ⲿ�ŘO���ʹdi/dt����һ�����y(c��)�õĂ��y(t��ng)SiC MOSFET�c����SBD��SiC MOSFET���_(k��i)�P(gu��n)���Ύ�һ�¡����y(t��ng)SiC MOSFET�c����SBD��SiCMOSFET�_(k��i)ͨ�p�ģ�Eon���քe��22mJ/pulse��21mJ/pulse���P(gu��n)���p�ģ�Eoff���t�քe��7.6mJ/pulse��6.0mJ/pulse��

�D7 �_(k��i)ͨ����(175����SBD�����m(x��)�����O��)

�D8 �P(gu��n)�ನ��(175����SBD�����m(x��)�����O��)

�D9 �_(k��i)�P(gu��n)�y(c��)ԇ�·

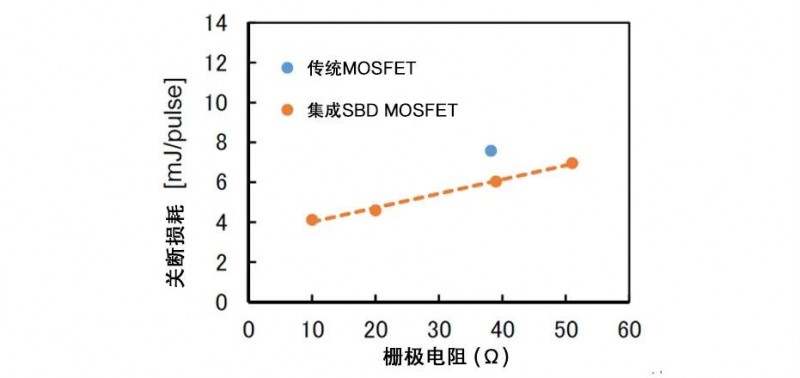

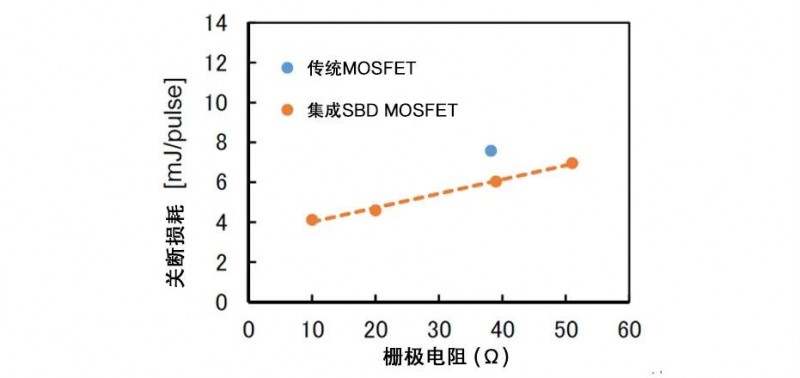

�D10�͈D11�鼯��SBD��SiC MOSFET Eon��Eoff�c�ŘO���֮�g���P(gu��n)ϵ��������Eon��Eoff�S���ŘO���Ľ��Ͷ����Խ������D12����y(t��ng)SiC MOSFETģ�K�c����SBD��SiC MOSFETģ�K��175��l���µķ���֏�(f��)������Ό�(du��)�ȣ������ϛ](m��i)�����@�IJ�����⣬���īI(xi��n)5���������y(t��ng)SiC MOSFET���w���O�ܕ�(hu��)���c������������SBD��SiC MOSFET����֏�(f��)��ΘO�������������˼���SBD��SiC MOSFET���Խ��ͷ���֏�(f��)�p�ġ�

�D10 Eon�c�ŘO�����P(gu��n)ϵ�D��Tj=175�棩

�D11 Eoff�c�ŘO�����P(gu��n)ϵ

�D12 ����֏�(f��)�������

4 �Y(ji��)Փ

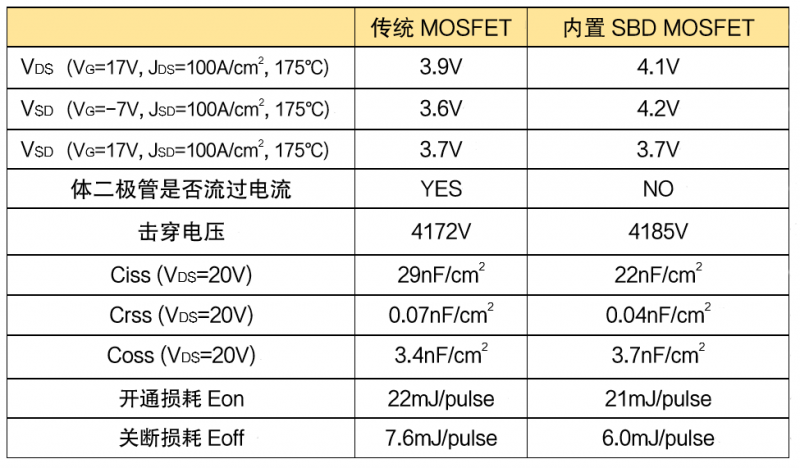

���ľ�3.3kV����SBD��SiC MOSFET�͂��y(t��ng)SiC MOSFET��늚��������ˌ�(du��)�������1��ʾ�����ߵ�늚����ԛ](m��i)�����@�IJ�����ڼ���SBD��SiC MOSFET����(hu��)�l(f��)���p�O�˻����������һ���߉�SiC����ģ�K���кܺõđ�(y��ng)��ǰ����

��1 ���y(t��ng)MOSFET�c����SBD��SiC MOSFET����(sh��)��(du��)��

�����īI(xi��n)

[1] http://www.mitsubishielectric.co.jp/news/2014/0430.html

[2] K.Hamada, et al., “3.3kV/1500A power modulesfor the world’s first all-SiC traction inverter”, Jpn. J.Appl. Phys. 54 (2015)04DP07.

[3] S.Hino, et al., “Demonstration of SiC-MOSFETEmbedding Schottky Barrier Diode for Inactivation of Parasitic Body Diode”,Materials Science Forum, vol.897 (2017) pp.477-482.

[4] T.Tominaga, et al., “Superior Switchingcharacteristics of SiC-MOSFET embedding SBD”, ISPSD 2019, pp.27-30.

[5] T.Tominaga, et al., “Investigation on theEffect of Total Loss Reduction of HV Power Mpdule by using SiC-MOSFET EmbeddingSBD”, ICSCRM 2019, Mo-P-43.

��0�l [�鿴ȫ��] �W(w��ng)���u(p��ng)Փ